はじめに

Xilinx搭載のFPGAボードで、ボード上のLEDをチカチカさせてみる。

xilinxのFPGAボードを使用するときはvivadoという開発環境を使用する。

意外と使い方が面倒なのでメモしていく。

環境

Arty S7 50 Rev.B

Linux mint

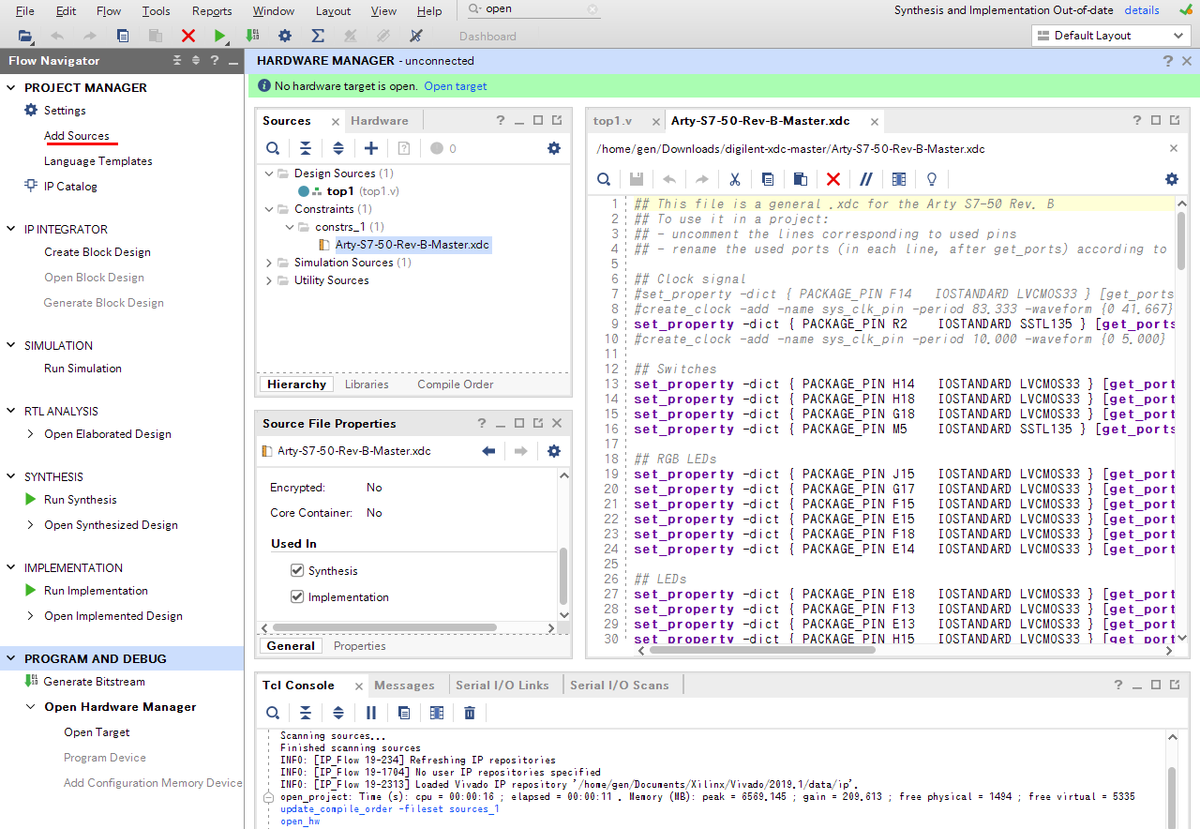

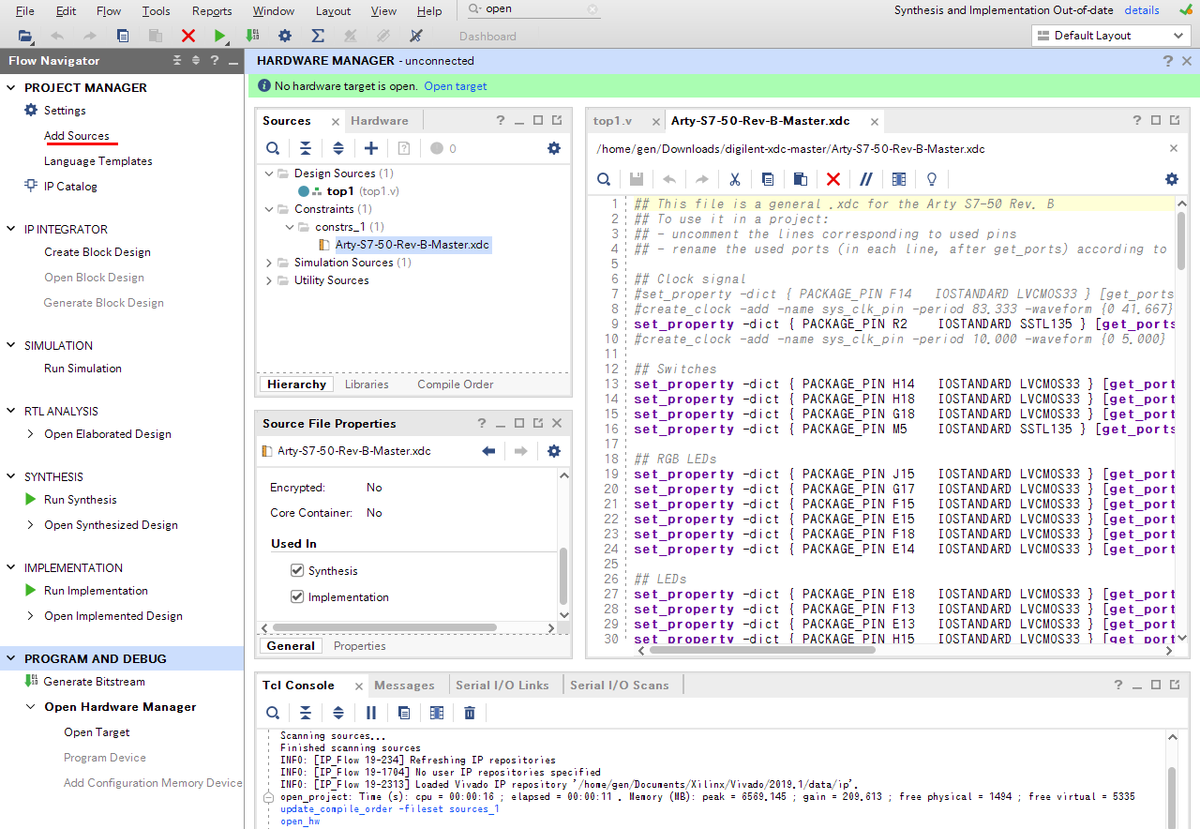

xdcファイルの読み込み

ザイリンクスデザイン制約(xdc)ファイルを読み込みます。

まずはArty S7のxdcファイルをダウンロードします。 github.com

ダウンロードしたら読みんでいきます。左のFlow Navigatorから

Add Sourcesをクリック

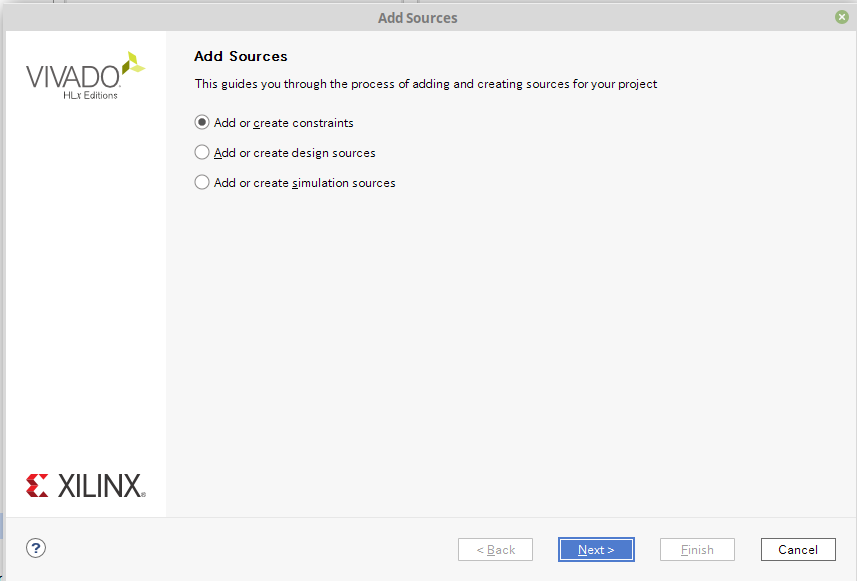

Add or crate constaraintsをクリック

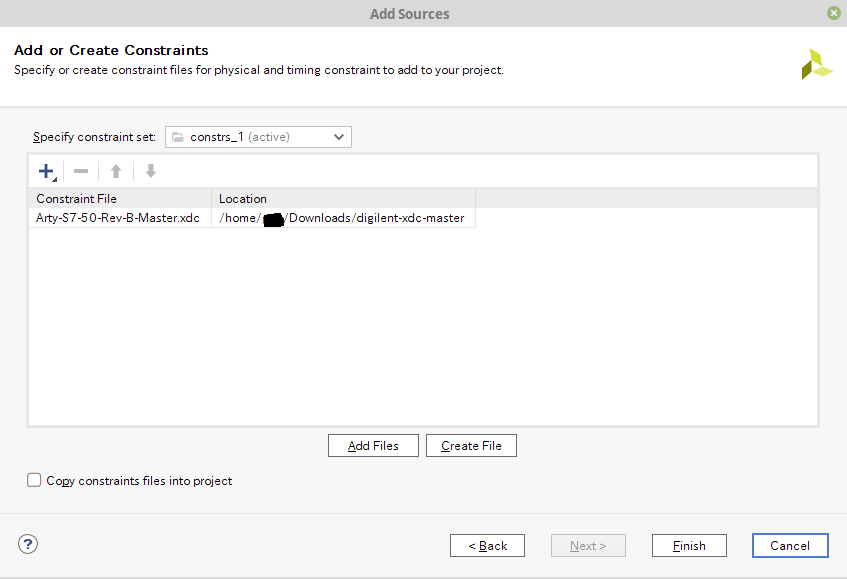

先程ダウンロードしたxdcファイルを

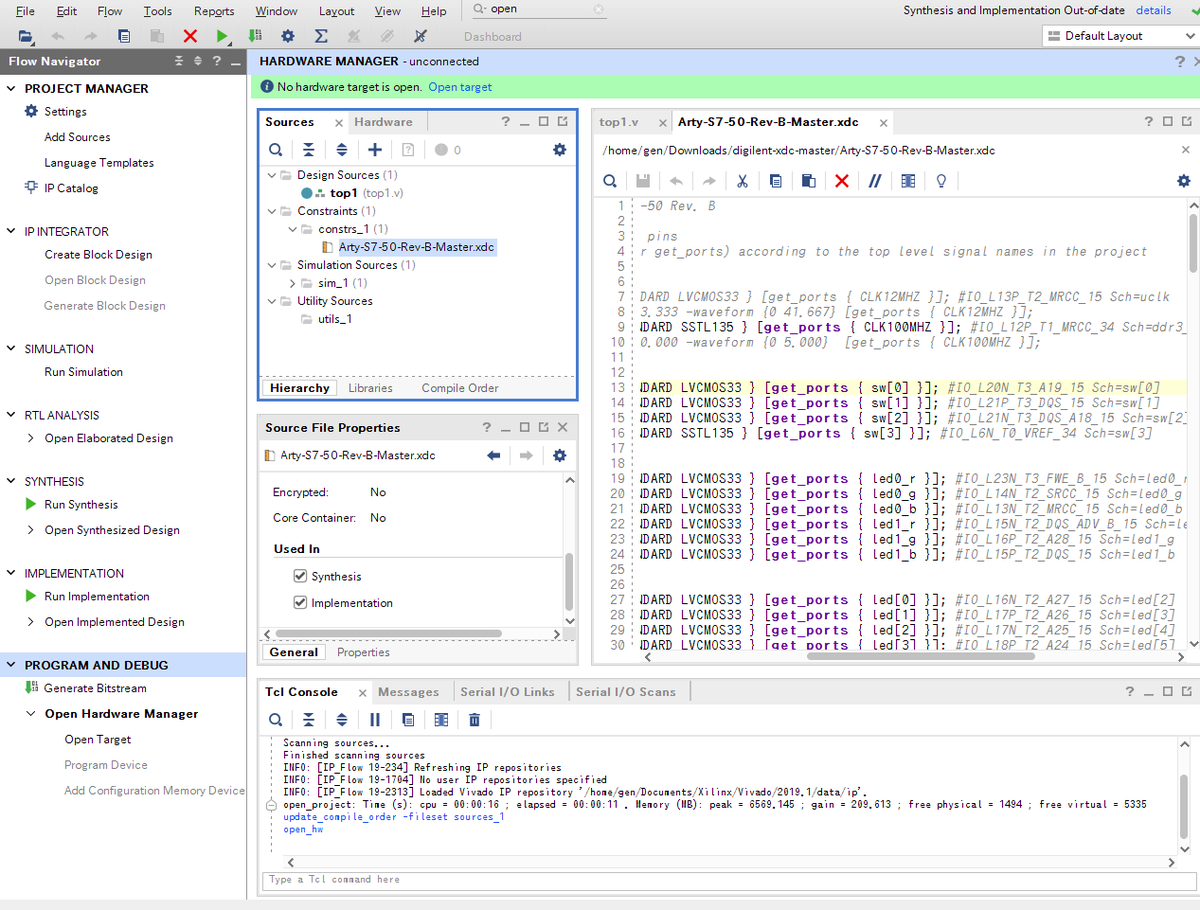

今回使うのはクロックとArty S7に搭載されているLED4個なので

対応するコードをコメントアウト化していく。

以下のコードがコメントアウトしていることを確認

以下のコードがコメントアウトしていることを確認

set_property -dict { PACKAGE_PIN R2 IOSTANDARD SSTL135 } [get_ports { CLK100MHZ }]; #IO_L12P_T1_MRCC_34 Sch=ddr3_clk[200]

## LEDs

set_property -dict { PACKAGE_PIN E18 IOSTANDARD LVCMOS33 } [get_ports { led[0] }]; #IO_L16N_T2_A27_15 Sch=led[2]

set_property -dict { PACKAGE_PIN F13 IOSTANDARD LVCMOS33 } [get_ports { led[1] }]; #IO_L17P_T2_A26_15 Sch=led[3]

set_property -dict { PACKAGE_PIN E13 IOSTANDARD LVCMOS33 } [get_ports { led[2] }]; #IO_L17N_T2_A25_15 Sch=led[4]

set_property -dict { PACKAGE_PIN H15 IOSTANDARD LVCMOS33 } [get_ports { led[3] }]; #IO_L18P_T2_A24_15 Sch=led[5]

ここまで来ればプログラムを書く準備ができた。

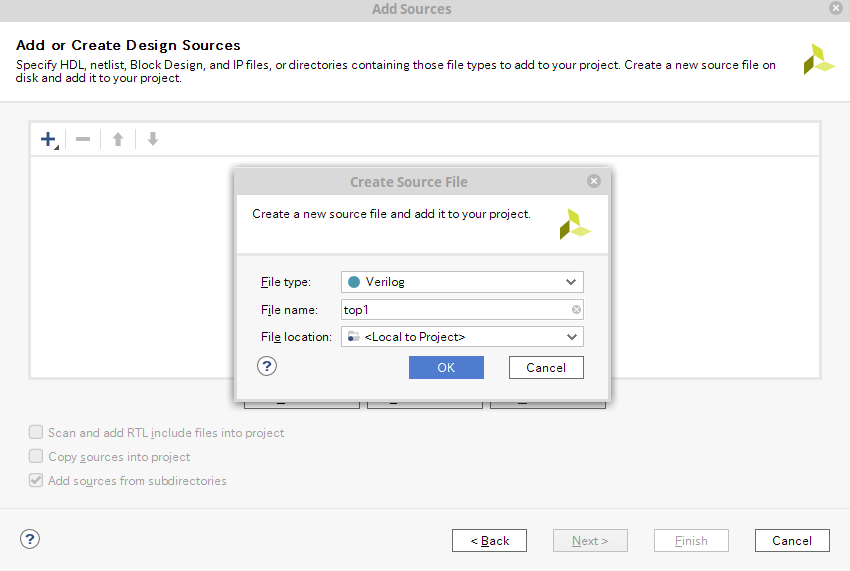

ソースコード

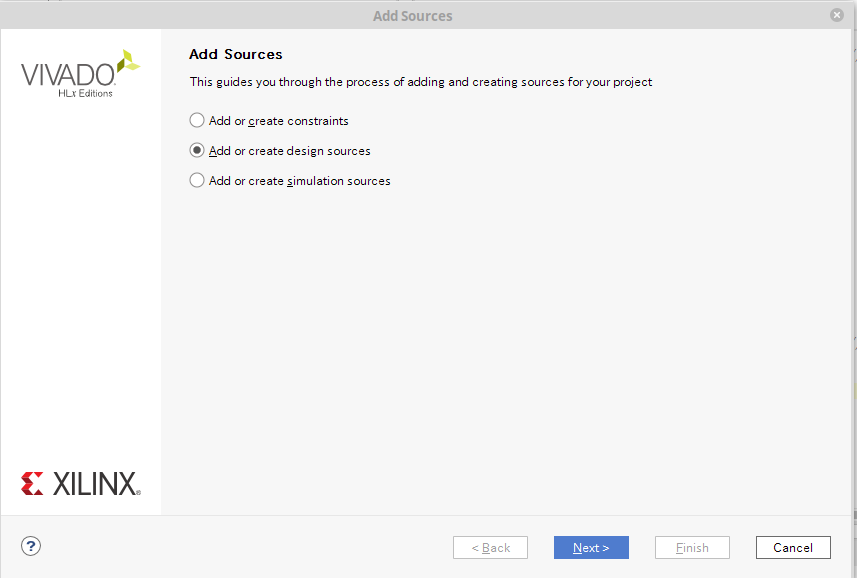

左のFlow NavigatorからAdd Sourcesを選択

Add create design sources をクリック

Create File を選択しファイルを作成。

言語はVerilogを使うので、Verilogを選択。

gisted073bd71b3751e415db4fcfbeeb2323

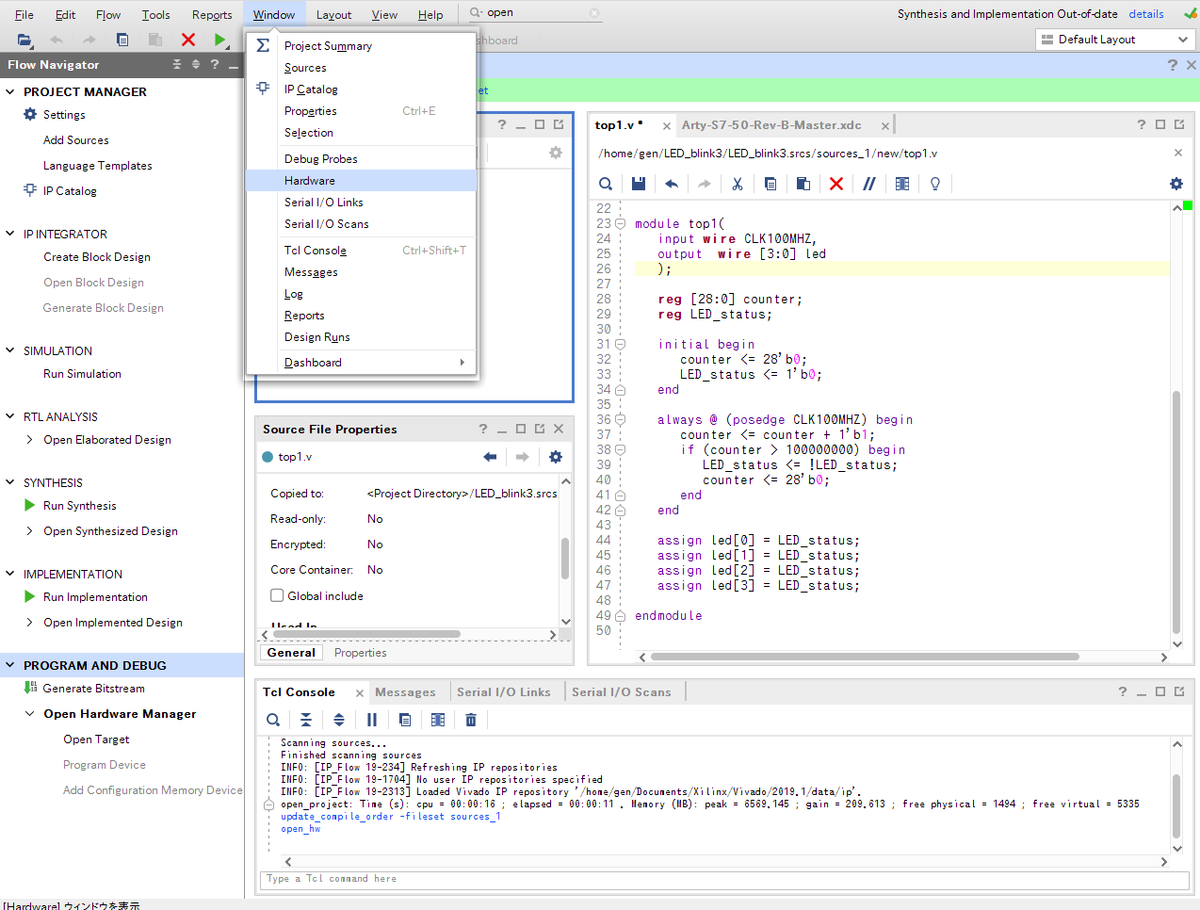

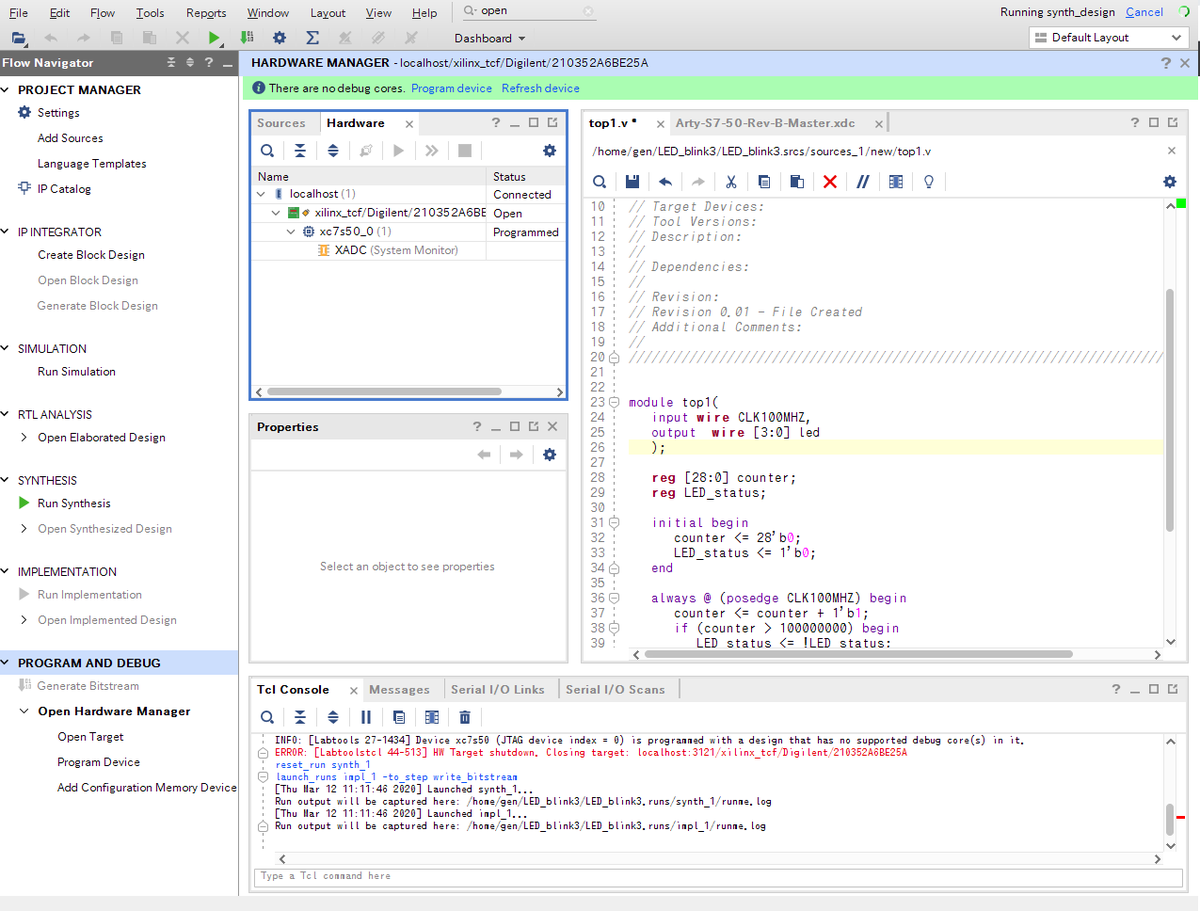

書き込み

まずはArty S7の読み込み

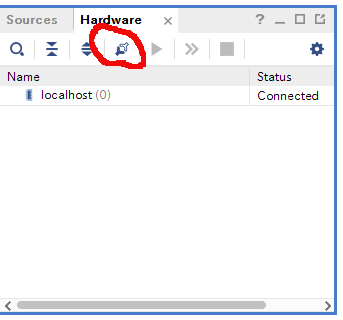

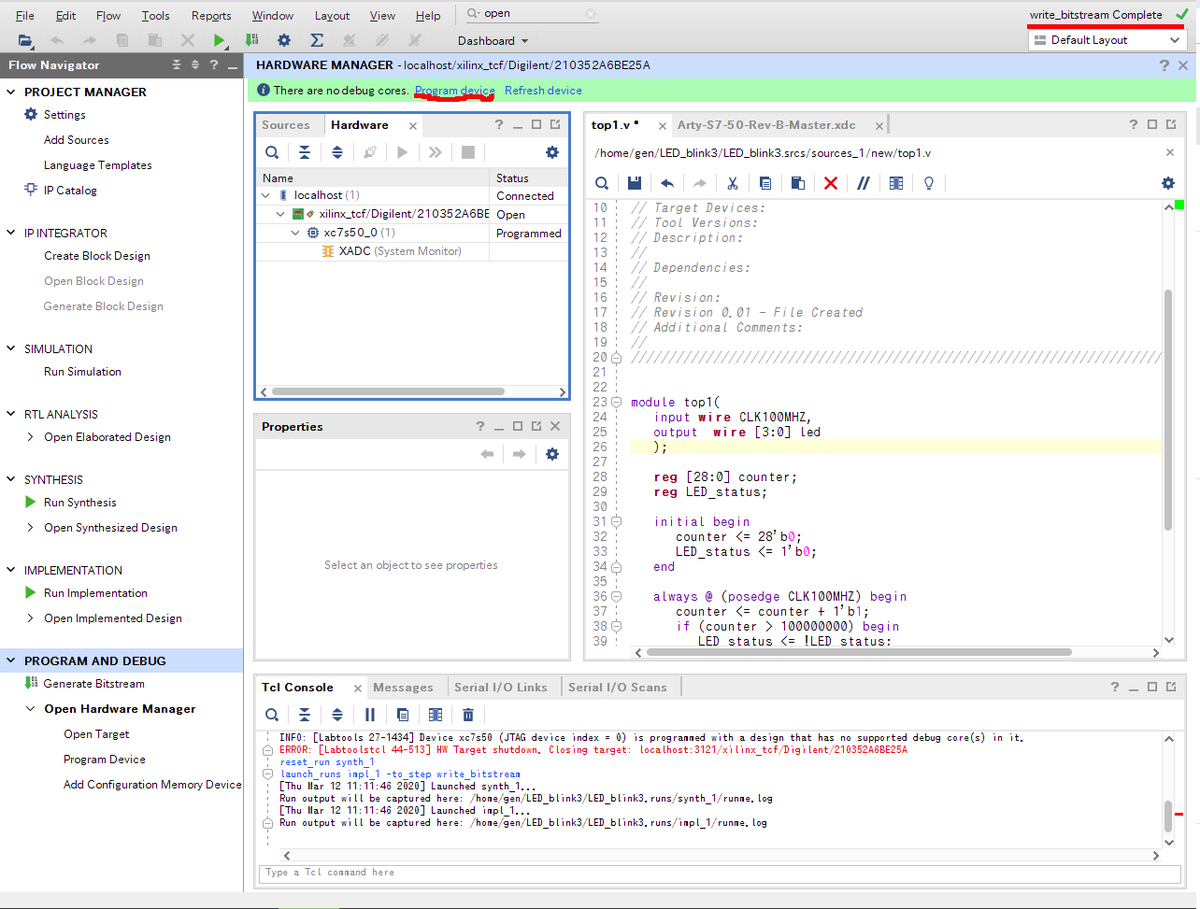

ハードウェアマネージャを開く

Autoコネクトを選択

Autoコネクトを選択

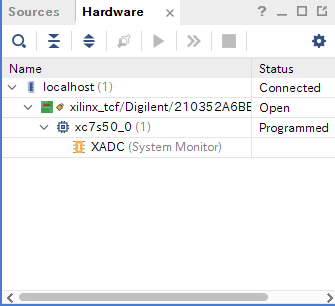

ハードウェアと接続が確立するとこんな表示が表示される。

ハードウェアと接続が確立するとこんな表示が表示される。

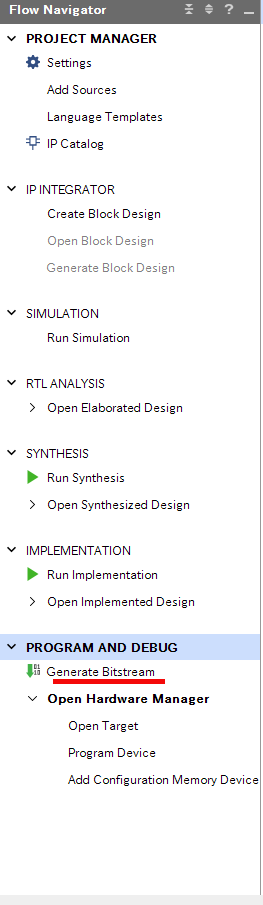

generate bitstreamをクリック

右上がくるくる回っていれば実行中

write_bitstream Compleateが画面の右上に表示されていることを確認したら

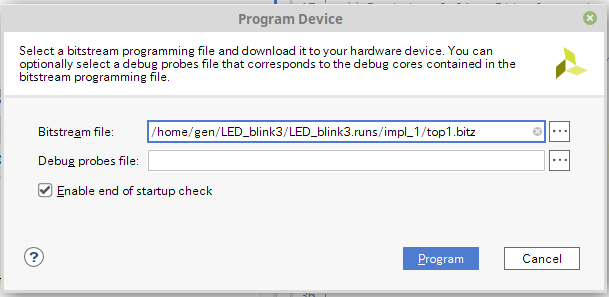

Programa deviceを選択する。

Programをクリックし書き込み

結果

参考文献

http://www.icrus.org/machida/product/verilog.pdf